פליפ פלופ

באלקטרוניקה ומעגלים אלקטרוניים, פליפ פלופ (בעברית: דְּלַגְלַג[1]) הוא מעגל רב־רטט דו־יציבי שמסוגל לשמור ערך של סיבית (bit) אחת.

בעבר נבנו מעגלי פליפ פלופ סביב שתי שפופרות ריק מסוג טריודה. מצב יציב ראשון היה כאשר שפופרת אחת הוליכה זרם חשמלי והשפופרת השנייה לא הוליכה זרם. המצב היציב השני היה הפוך. במחשב הראשוני אניאק השתמשו בשפופרת טריודה כפולה מדגם 6SN7 למעגל פליפ פלופ אחד לשם זיכרון של ביט אחד. עם המצאת הטרנזיסטור בשנות ה־50 של המאה ה־20, נבנו המעגלים סביב שני טרנזיסטורים שהחליפו את הטריודות. עם פיתוחם של המעגלים המשולבים בשנות ה־60 של המאה ה־20, יוצרו שבבים המכילים פליפ פלופים רבים.

הפליפ הפלופ האלקטרוני הראשון הומצא בשנת 1919 על ידי ויליאם אקלס (William Eccles) ופ. ו. ג'ורדן (F. W. Jordan), ולכן בתחילה הוא נקרא מעגל מעורר אקלס־ג'ורדן.

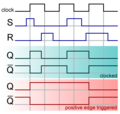

הפליפ פלופ הקלאסי מסוג S-R מקבל 2 אותות: "עבור למצב 1" (Set), "עבור למצב 0" (Reset) ומוציא 2 אותות: המצב (Q) והיפוך המצב.

במערכות סינכרוניות הפליפ פלופ מקבל גם אות שעון. במערכות אלה נפוצות 4 סוגים: T (קיצור של Toggle), S-R (קיצור של Set-Reset), J-K (על שם הממציא), ו־D (קיצור של Delay). מצב הפליפ פלופ נקבע בכל מחזור שעון מחדש על פי משוואת המצב שלו. משוואה זו מגדירה תוצאת על פי ערכי הכניסות או ערך המוצא הנוכחי .

היסטורית, השם "פליפ פלופ" שימש לתיאור הן של רכיבים סינכרוניים והן של רכיבים א-סינכרוניים. בשנים מאוחרות יותר נשמר לעיתים השם לרכיבים סינכרוניים בלבד - כלומר, כאלו המשנים את המוצא רק בעליית או בירידת אות השעון (לפי החלטת היצרן). מעבר של השעון מ־0 לוגי ל־1 לוגי או להפך נקרא מעבר אקטיבי של השעון, או שפה דוגמת של השעון.

סוגי פליפ פלופ

[עריכת קוד מקור | עריכה]פליפ פלופ T

[עריכת קוד מקור | עריכה]

אם כניסה T בפליפ פלופ גבוהה, הפליפ פלופ הופך את המוצא. אם כניסה T נמוכה הוא שומר על הערך הקודם של היציאה. דלגלג זה מתנהג כשער לוגי XOR. ההתנהגות הזאת מתוארת על פי המשוואה הבאה:

וזאת טבלת האמת שלו:

| T | Qnext |

| 0 | |

| 1 |

פליפ פלופ S-R

[עריכת קוד מקור | עריכה]

פליפ פלופ Set/Reset מוציא ערך לוגי גבוה אם כניסת Set שלו גבוהה וכניסת Reset נמוכה בשפה הדוגמת של השעון. הפליפ פלופ מוציא ערך לוגי נמוך אם כניסת Reset שלו גבוהה וכניסת Set נמוכה בשפה הדוגמת של השעון. אם שתי הכניסות Set ו־Reset נמוכות הפליפ פלופ שומר על ערכו הנוכחי והמוצא לא משתנה בשפה הדוגמת של השעון (הפליפ פלופ זוכר את המוצא הקודם). אולם, אם שתי הכניסות Set ו־Reset גבוהות בשפה הדוגמת של השעון, המוצא לא מובטח. זאת טבלת האמת של פליפ פלופ S-R:

הטבלה הבאה מראה את ערך המוצא לפני עלית השעון כאילו היה כניסה נוספת:

| S | R | Qnext |

| 0 | 0 | |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | לא־יציב |

באחריות מתכנן המעגל להבטיח שלא ייווצר מצב בו S=R=1. בהינתן תנאי זה, בדרך כלל נמנעים מכתיבת משוואה אופיינית לפליפ פלופ S-R. קיימים חיבורי Master-Slave שונים של פליפ פלופים מסוג S-R שמשיגים תוצאות שונות, בדרך כלל כדי להימנע ממצב שבו S=R=1 ולהביא להתנהגות דטרמיניסטית.

-

דיאגרמת מעברים של פליפ פלופ S-R

-

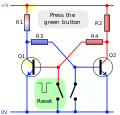

דיאגרמה אינטראקטיבית של פליפ-פלופ S-R (יש ללחוץ על התמונה להפעלה.

R1, R2 = 1 kΩ, R3, R4 = 10 kΩ -

מימוש פליפ פלופ S-R בעזרת שערי NOR

פליפ פלופ J-K

[עריכת קוד מקור | עריכה]

פליפ פלופ J-K דומה לפליפ פלופ S-R, אך ההבדל ביניהם הוא במצב שבו שתי הכניסות שוות ל־1. פליפ פלופ J-K מפרש מצב זה בתור היפוך הכניסה. בפירוט, הצירוף J=1, K=0 קובע את מוצא הפליפ פלופ ב־1 לוגי, הצירוף J=0, K=1 מאפס את מוצא הפליפ פלופ, והצירוף J=K=1 הופך את מוצא הפליפ פלופ (קובע את המוצא החדש בתור ההופכי של המוצא הישן. אם קובעים שתמיד J=K הפליפ פלופ הופך להיות פליפ פלופ מסוג T.

המשוואה האופיינית של פליפ פלופ J-K היא:

וטבלת האמת שלו היא:

| J | K | Qnext |

| 0 | 0 | |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 |

ראשי התיבות של הפליפ פלופ מפורשים בהומור בתור Jump-Kill.

פליפ פלופ D

[עריכת קוד מקור | עריכה]

פליפ פלופ מסוג D (קיצור ל־Data או ל־Delay) הוא בעל כניסה אחת שמועברת למוצא בשפה הדוגמת של השעון, ללא תלות במוצא הנוכחי. אם D=1, בשפה הדוגמת של השעון המוצא יהיה 1 ואם D=0 בשפה הדוגמת של השעון המוצא יהיה 0. התנהגות הפליפ יכולה להתפרש כהשהיה, כי המידע עובר דרך הפליפ פלופ בהשהיה של מחזור שעון מאז שהגיע לכניסתו.

המשוואה המאפיינת את הפליפ פלופ היא:

וטבלת האמת שלו היא:

| D | Qnext |

| 0 | 0 |

| 1 | 1 |

שימושים

[עריכת קוד מקור | עריכה]הפליפ פלופ יכול לשמור סיבית אחת של מידע. לפיכך ניתן לממש אוטומט סופי (מכונת מצבים) באמצעות מספר פליפ פלופים לזכירת המצב הנוכחי של המכונה. באמצעות לוגיקה צירופית יחושב המוצא והמצב הבא כפונקציה של הכניסות והמצב הנוכחי על מנת לבצע את פעולת האוטומט כפי שתוכננה.

במחשב נהוג לקבץ מספר פליפ פלופים לפי גודל מילת המעבד לכדי אוגרים. האוגרים משמשים לשמירת מצב המעבד ולאחסון מיידי של האופרנדים לפעולותיו, בין אם אלה ערכים מספריים, מונים, תווים ASCII או נתונים מסוגים רבים נוספים. אוגרים בודדים יכולים להיות ממומשים גם שלא כחלק ממעבד מחשב. אוגר זיזה, למשל, הוא אוטומט סופי בעל שימושים רבים בהנדסת חשמל לרבות אפליקציות בתורת הקודים ובקריפטוגרפיה.

פליפ פלופ D מייצג סיבית אחת במספר בינארי כחלק מן האוגר.

פליפ פלופ T שימושי לספירה. בשפה הדוגמת של השעון הפליפ פלופ הופך את המוצא אם כניסת T שלו היא 1. המוצא מפליפ פלופ אחד יכול להתחבר לכניסת השעון של פליפ פלופ אחר וכן הלאה. כאשר המוצא הסופי של המעגל הוא רצף של סיביות שהן מוצאי פליפ פלופים, מתקבל מספר בינארי שמייצג את מספר מחזורי השעון שעברו. המספר המקסימלי הוא כאשר n הוא מספר הפליפ פלופים בהם משתמשים.

אחת הבעיות במונה כזה (שנקרא Ripple counter) היא שהיציאה לא תקפה בזמן שהשינוי בכניסה מתפשט דרך המעגל. קיימים שני פתרונות לבעיה זו. אחד מהם הוא לדגום את מוצא המעגל רק בזמן שהוא תקף (אפשר למשל לשים פליפ פלופ D במוצא). פתרון אחר הוא להשתמש במעגל מסוג אחר שנקרא מונה סינכרוני. המימוש שלו מסובך יותר כדי להבטיח שהמוצאים של המונה משתנים בו זמנית ברגע ידוע מראש.

מחלק תדר: שרשרת של פליפ פלופים מסוג D כמו שתוארה לעיל מחלקת את התדר פי 2n, כאשר n הוא מספר הפליפ פלופים בין הכניסה ליציאה.

תיזמון ומטה־סטביליות

[עריכת קוד מקור | עריכה]פליפ פלופ סינכרוני מועד לבעיה שנקראת מטה־סטביליות שמתרחשת כשכניסת הנתונים משתנה בזמן השפה הדוגמת של השעון. התוצאה היא שהפליפ פלופ עלול להתנהג בצורה לא צפויה. עלול לקחת זמן רב יותר עד שהיא תעבור לערך לוגי חוקי כלשהו, אך ערך זה עלול להיות לא נכון. במערכות מחשב מצב זה עלול לגרום לקריסת תוכנה והשחתת מידע.

ניתן למנוע מטה־סטביליות אם מוודאים שכניסות המידע תקפות בפרק זמן כלשהו לפני ואחרי השפה הדוגמת, שנקראים זמן setup (מסומן tsu) וזמן hold (מסומן th) בהתאמה. זמנים אלה ניתנים בדפי המידע שמספק היצרן, והם בדרך כלל בין כמה ננו־שניות לכמה מאות ננו־שניות ברכיבים מודרניים. כל הזמנים במעגל סינכרוני נמדדים ביחס לשפה הדוגמת של השעון.

אולם לא תמיד ניתן לעמוד בתנאי setup ו־hold כי כניסת הפליפ פלופ יכול להתחבר לאות שעלול להשתנות בזמן שלא בשליטת המתכנן. במצב כזה, הדבר הטוב ביותר שהמתכנן יכול לעשות הוא להפחית את הסיכוי לתקלה עד מידה מסוימת, שתלויה בדרישות האמינות של המעגל. שיטה אחת למנוע מטה־סטביליות היא לחבר כמה פליפ פלופים בשרשרת, כך שהמוצא של פליפ פלופ אחד מזין את המבוא של הפליפ פלופ הבא ולכולם שעון משותף. בשיטה זו הסיכוי למטה־סטביליות יורד לערך זניח, אבל אף פעם לא לאפס.

קיימים פליפ פלופים עמידים במיוחד בפני מטה־סטביליות. בהם זמני setup ו־hold הם קצרים מאוד, אבל גם הם לא פותרים את הבעיה לחלוטין. זה מפני שמטה־סטביליות היא לא רק עניין של תכנון המעגל. כששינויי השעון והמידע סמוכים זה לזה, מתרחש מרוץ מידע והפליפ פלופ מוכרח להכריע מה התרחש קודם. גם אם הפליפ פלופ יהיה מהיר מאוד, אם שינוי המידע והשעון יהיו סמוכים מאוד קיים סיכוי שהפליפ פלופ לא יכריע מי התרחש קודם ויכנס למצב מטה־סטבילי. לכן לא ניתן לבנות פליפ פלופ חסין בפני מטה־סטביליות.

זמן חשוב אחר נקרא זמן השיהוי מהשעון למוצא (שמסומן tpC-Q) שהוא הזמן שלוקח לפליפ פלופ לשנות את המוצא אחרי השפה הדוגמת. לעיתים זמן שינוי המוצא מערך נמוך לגבוה (tplh) שונה מזמן שינוי המוצא מערך גבוה לנמוך (tphl).

זמן חשוב נוסף הוא שיהוי הזיהום (contamination delay שמסומן tcC-Q) שהוא הזמן שמובטח שמוצא הפליפ פלופ נשאר בערכו הקודם לאחר השפה הדוגמת של השעון. לאחר זמן זה מוצא הפליפ פלופ עלול להשתנות ולהיות לא תקף. אולם מובטח שלאחר שעבר זמן tpC-Q במוצא יופיע ערך לוגי תקף ונכון.

כשמחברים כמה פליפ פלופים ברצף כשביניהם לוגיקה צירופית (CL) ומחזור שעון באורך Tclk, חשוב להבטיח שבמסלול הארוך ביותר בין שני פליפ פלופים יתקיים התנאי הבא:

ובמסלול הקצר ביותר מוכרח להתקיים התנאי הבא: